Ia-64 Application Instruction Set Architecture Guide Revision 1

Di: Ava

The disclosures show a thoroughly modern instruction set with a range of multimedia instructions and prefetch capabilities. Although IA-64 includes many RISC concepts, the architects added some rather complicated and special-ized instructions. Concerns remain, however, about code density and just how much of an advantage these new fea-tures will provide over a standard lApplication Instruction Set Architecture Guide – Complete disclosure of IA-64 application architecture lResult of the successful collaboration between Intel and HP Internet, Enterprise, and Workstation IA-64 Solutions Enterprise Technology Centers Application Solution Centers Operating Systems Tools

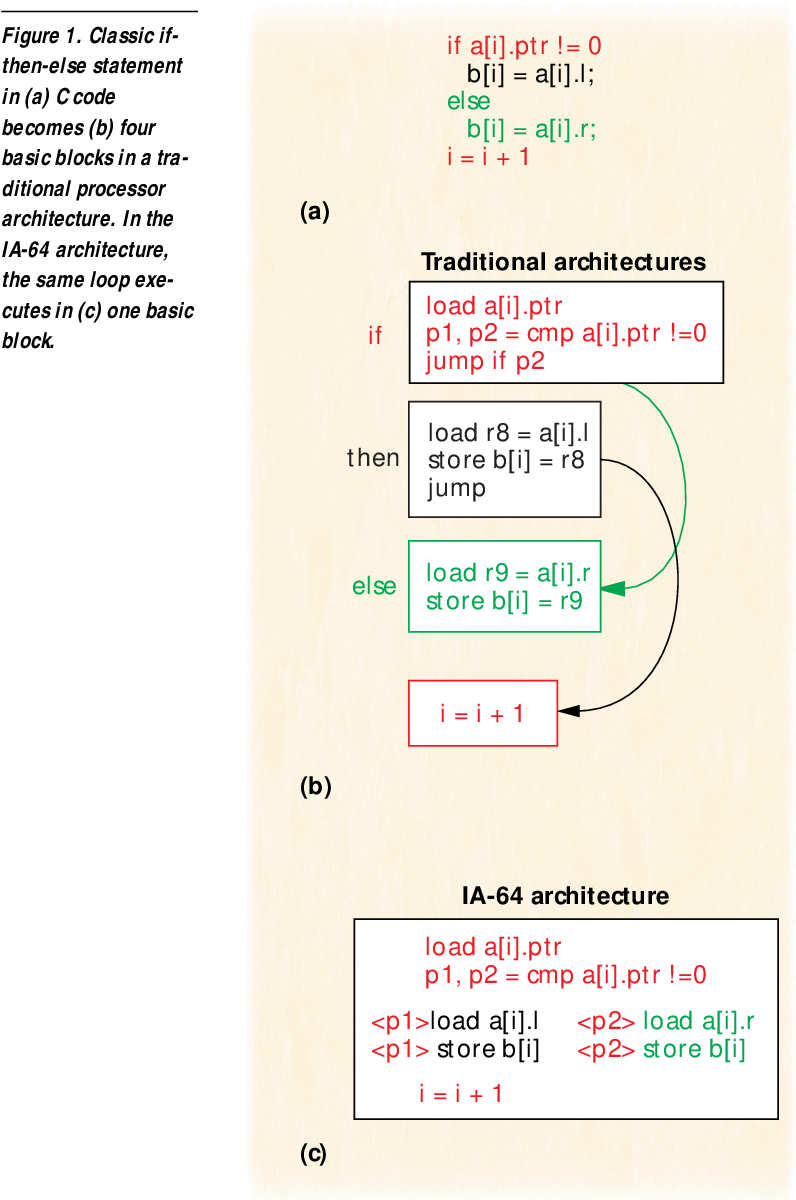

Itanium – An EPIC ArchitectureITANIUM An Architecture The IA-64 architecture uses explicit information about instruction grouping, pre-fetching, predication and speculative execution to help overcome the limitations of today’s RISC (Reduced Instructions Set Computing) architectures.

Intel Itanium Architecture

Computer Science & Engineering University of Washington Box 352350 Seattle, WA 98195-2350 (206) 543-1695 voice, (206) 543-2969 FAX

Three 41-bit instructions are packed into a 128-bit word; the remaining 5 bits used to guide the hardware on available parallelism. IA-64 also introduced speculative loads [21]. Chapter 10, “IA-64 Operating System Interaction Model with IA-32 Applications” defines the operation of IA-32 instructions within the IA-64 System Environment from the perspective of an IA-64 operating system.

Notice:The Intel®64 and IA-32 architectures may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are documented in the specification updates.

Intel AVX, Intel AVX2 and many Intel AVX-512 instructions are covered in Intel® 64 and IA-32 Architectures Software Developer’s Manual. The reader can refer to them for basic and more background information related to various features referenced in this document.

How to Use the System V ABI for Intel® ItaniumTM Processors The Itanium architecture supports a 64 bit instruction set and also provides compatibility with the IA-32 instruction set. Binaries using the Itanium architecture instruction set may program to either a 32-bit model, in which the C data types int and long and all pointer types are 32-bit objects (ILP32); or to a 64-bit model, in Technically-oriented PDF Collection (Papers, Specs, Decks, Manuals, etc) – pdfs1/AMD64 Architecture Programmer’s Manual – Volume 1 – Application Programming (24592, r3.21, Oct-2013).pdf at master · cryopie/pdfs1 Volume 2A: Instruction Set Reference, A-M NOTE: The Intel 64 and IA-32 Architectures Software Developer’s Manual consists of five volumes: Basic Architecture, Order Number 253665; Instruction Set Reference A-M, Order Number 253666; Instruction Set Reference N-Z, Order Number 253667; System Programming Guide, Part 1, Order Number 253668; System

See the description of the CPUID instruction in Chapter 3, “Instruction Set Reference, A-L,” of the Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volume 2A. IA-64 (Intel Itanium architecture) is the instruction set architecture (ISA) of the discontinued Itanium family of 64-bit Intel microprocessors. The basic ISA specification originated at Hewlett-Packard (HP), and was subsequently implemented by Intel in collaboration with HP. Understanding the IA-64 Architecture Gautam Doshi Senior Architect IA-64 Processor Division Intel Corporation August 31,’99 – September 2,’99 Today’s Architecture Challenges IA-64 Architecture Performance Features High-end Application Characteristics End User Benefits of IA-64 Features Programmer programs in high level lang.

Introducing the IA-64 architecture

Starting in 1994, the joint HP-Intel IA-64 architecture team leveraged this prior work and incorporated feedback from compiler and processor design teams to engineer a powerful initial set of features. They also carefully designed the instruction set to be expandable to address new technologies and future workloads. Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or The MIPS32 and MIPS64 Instruction Set Architectures define a compatible family of instructions that handle 32-bit data and 64-bit data (respectively) within the framework of the overall MIPS Architecture.

Manuals on Itanium architecture Intel Itanium Architecture Software Developer’s Manual, Volume 1: Application Architecture, revision 2.2, 2006, 24531705.pdf (4885619 bytes); Volume 2: System Architecture, revision 2.2, 2006, 24531805.pdf (10379089 bytes); Volume 3: Instruction Set Reference, revision 2.2, 2006, 24531905.pdf (11299570 AMD – GCN3 Instruction Set Architecture – Graphics Core Next Architecture, Generation 3 (Revision 1.0, March 2015).pdf Cannot retrieve latest commit at this time. Technically-oriented PDF Collection (Papers, Specs, Decks, Manuals, etc) – pdfs/AMD – AMD64 Architecture Programmer’s Manual – Volume 1 – Application Programming – Rev 3.22 – Dec 2017 (24592).pdf at master · tpn/pdfs

Starting in 1994, the joint HP-Intel IA-64 architecture team leveraged this prior work and incorporated feedback from compiler and processor design teams to engineer a powerful initial set of features. They also carefully designed the instruction set to be expandable to address new technologies and future workloads. Lecture Design justification pactkeynote.pdf Diagram of Itanium microarchitecture ia64-microarch.pdf A more detail of ia-64 architecture archSysSoftware.pdf General feature of Itanium idfisa.pdf IA-64 instruction set (assembly language) ia64-tutorial.pdf Compiler for ia-64 isca_compiler2.pdf

Intel® IA-64 Architecture Software Developer’s Manual Volume 2: IA-64 System Architecture Revision 1.1

Understanding the IA-64 Architecture Gautam Doshi Senior Architect IA-64 Processor Division Intel Corporation August 31,’99 – September 2,’99 Today’s Architecture Challenges IA-64 Architecture Performance Features High-end Application Characteristics End User Benefits of IA-64 Features Programmer programs in high level lang.

An Overview of IA-64 Architectural Features and Compiler Optimization

See the description of the CPUID instruction in Chapter 3, “Instruction Set Reference, A-L,” of the Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volume 2A. Intel® Itanium® Processor Reference Manual for Software Development – This document (Document number 245320) describes model-specific architectural features incorporated into the Intel® Itanium® processor, the first processor based on the Itanium architecture. Intel® 64 and IA-32 Architectures Software Developer’s Manual – This set of manuals describes the Intel 32-bit

•Itanium Instruction Mem Faults– The following additional Itanium memory faults can be generated on each virtual page referenced when fetching IA-32 or MMX technology or SSE instructions for execution: • Alternative instruction TLB fault • VHPT instruction fault • Instruction TLB fault • Instruction Page Not Present fault Intel Architecture 64 bit. The first document describing the new instruction set was published by Intel in May 1999. The name IA-64 was published beforehand, and some of the features were known beforehand (predication and wide-issue were discussed in December 1997 on comp.arch). Itanium processors natively supported the x86 instruction sets, but they stripped the x86 rMove the complexity of resource allocation and instruction scheduling to the compiler

Intel AVX, Intel AVX2 and many Intel AVX-512 instructions are covered in the Intel® 64 and IA-32 Architectures Software Developer’s Manual. The reader can refer to them for basic and more background information related to various features referenced in this document. What does the latest ARM ARM include? It describes the registers, instructions, instruction encodings, exception model, virtual memory model (including cache support) and memory management, as well as the debug architecture. At a high level, ARMv8-A describes both a 32-bit and 64-bit architecture, respectively called AArch32 and AArch64.

The IA-64 Intel® IA-64 Architecture Software Developer’s Manual defines the IA-64 application instruction set architecture. Programs intended to execute directly on an IA-64 processor use the instruction set, instruction encodings, and instruction semantics defined in the Intel® IA-64 Architecture Software Developer’s Manual. Intel® 64 and IA-32 Architectures Software Developer’s Manual Volume 3C: System Programming Guide, Part 3 NOTE: The Intel®64 and IA-32 Architectures Software Developer’s Manualconsists of nine volumes: Basic Architecture, Order Number 253665; Instruction Set Reference A-M, Order Number 253666;

Ref. # 319433-038 v -035 • Updated Table 1-1 “Recent Instruction Set Extensions / Features Introduction in Intel® 64 and IA-32 Processors” to list the AVX512_VNNI instruction set architecture on a separate line due to presence on future processors available sooner than previously listed. • Updated CPUID instruction in various places. • Removal of NDD/DDS/NDS

Chapter 10, “IA-64 Operating System Interaction Model with IA-32 Applications” defines the operation of IA-32 instructions within the IA-64 System Environment from the perspective of an IA-64 operating system. The IA-64 architecture was designed to overcome the performance limitations of today’ s architectures and provide maximum headroom for the future. To achieve this, IA-64 includes an array of innovative features to extract greater instruction level parallelism including: speculation, predication, large register files, a register stack, advanced branch architecture, and many

- Icd-10-Cm Diagnosis Code Z96.65

- Ice Epoxy Ice Cast 1.89 L Crystal Clear Resin

- Icare Surgical Centre – iCare Surgical Centre, Ottawa, ON

- I7 7700 Gtx 1050Ti Asus Strix, Power Consumption

- Ibn Lokmat News Private Limited

- I May Be Some Time | ALBUM REVIEW: Million Moons

- Ibm Lanza Su Ordenador Cuántico Más Potente Con 433 Qubits

- Iced Sugar Cookie Latte , Iced Sugar Cookie Latte Recipe

- I Live Alone |Episode 498|Variety Show Korea

- I Went To All I Got Was This Tshirt

- I Just Can’T Wait To Be King Karaoke

- I Would Like You To Do Something?

- I Want To Know How To Update Office 2016 Manually

- I’Ve Created A Dining Plan Pocket Menu For Y’All