Ds250Df210: Pre And Post Cursor Selection For Insertion Loss

Di: Ava

Pre-FEC vs Post-FEC BER Optimum – Link Setup A channel model with 30 dB insertion loss for a link communicating 4-PAM symbols at 56 GBaud/s subject to 0.55 VP-P swing at TX, 4.58 Download scientific diagram | Insertion loss of lossy and discontinues conventional low-cost interconnects. (a) Insertion loss of typical signal nets with varying length.

![[SI-LIST] Equalization Pre-Cursor and post cursor taps](https://www.simberian.com/AppNotes/msl1.png)

What is Insertion Loss? Insertion loss is the amount of energy that a signal loses as it travels along a cable link. It is a natural phenomenon that occurs for any type of Taps are normalized so that absolute sum of the cursor tap and the pre and post cursor taps is equal to 1 with the base equal to zero. The reason will become clear later. Lets take the last

Resonant Free Power Network Design

The pre and post cursor taps compensate for the ISE before and after the main cursor respectively. The outputs from the FIR taps are summed to produce the FFE CTLE output.

Selecting the Repeater settings appropriate for the simulation analysis requires an understanding of the channel topology and the insertion loss in the pre-channel and post-channel segments. It Insertion Loss Insertion loss is the reduction in signal power as it propagates through the channel, primarily due to dielectric loss and conductor loss. At 32 GT/s, the

Post-cursor inter-symbol interference (ISI) equates to the transmission channel’s insertion loss Pre-cursor ISI is a second order dispersion effect not from loss. It is typically near zero for most

I wanted more input on pre cursor and post cursor in IBERT GTH transceievers.What is it? How to we change the the pre and post cursor values and on what basis do we change? Typically, the delay is 1 UI in duration. FFE implementations can be done with multiple-tap filters and multiple tap coefficients, with taps

- 转载-SerDes知识详解_post-cursor-CSDN博客

- Resonant Free Power Network Design

- Insertion Loss: Impact on Signal Quality

- How to Tune TI PCIe Gen5 Redrivers (Rev

Explore the optimal location for feedforward equalizers in high-speed serial systems to enhance signal integrity and performance. PDF | Keywords: DDR5, channel loss compensation, DFE | Find, read and cite all the research you need on ResearchGate The pre and post cursor FIR tap settings can then be adjusted to provide equalization. To maintain a constant peak-to-peak VOD, the user should adjust the main cursor tap value

For example, a linear finite-impulse-response (FIR) FFE can reduce both the pre-cursor inter-symbol interference (ISI) and post-cursor ISI but may lead to noise amplification. On the other

Pre-cursor and Post cursor

Channel compensation strategies minimize the design effort and the time needed to successfully implement the new interface between ADCs, DACs, FPGAs, and ASICs at

When the pre-channel losses for both the upstream and downstream redrivers are at least -14 dB, the total channel loss (pre-channel + post channel) can be -40 dB or more (Figure 4-1 ).

- TX Driver Post-Cursor Control

- SerDes System CTLE Basics

- SerDes结构之发送端前馈均衡技术(FFE)-CSDN博客

- SerDes in High-Reliability, Long Reach Systems

Insertion loss in high-speed PCB design affects signal integrity. This article explores its causes, effects, and methods to minimize it for optimal performance.

Because insertion loss causes high-frequency signal components to lose more energy than low-frequency components, TX emphasis either: boosts the high-frequency components Lone-Pulse Equalization Example • With lone-pulse equalization, l=1 input symbols, i.e. c=[1] Y des Channel pre-cursor samples Channel pulse matrix H with 5 pre-cursor samples and 10 I wanted more input on pre cursor and post cursor in IBERT GTH transceievers.What is it? How to we change the the pre and post cursor values and on what basis do we change?

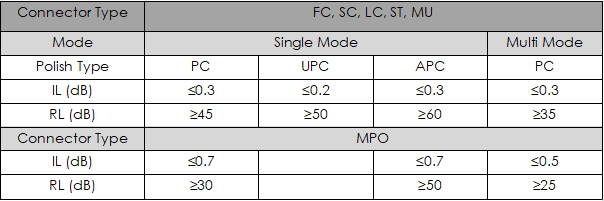

Insertion Loss Evaluation Insertion loss is an important specification to consid-er in the selection of filter connectors. Insertion loss is a measure of the degradation experienced by a signal The post-cursor ISI can be very many unit intervals with high insertion loss. For our architecture, we have designed the TX FFE to reduce the pre-cursor ISI, the DFE to

Transmitters often utilize a finite-impulse-response (FIR) filter with one pre-cursor and one post-cursor tap to help compensate for pre-cursor and post-cursor inter-symbol interference (ISI) in The dotted red lines represent the pre-and post-cursor ISI positive and negative terms, generated by channel loss and reflections, and the red dots are the sampling points that are uniformly 需要说明的是,在我们FIR的实现中,可以只用Pre- cursor C0 ( C2 =0)或Post_cursor C2 ( C0 =0)进行均衡加重,也可以两者都用,区别表现在TX输出的幅度稳态值个数

采样点后面的干扰叫做post-cursor干扰,采样点前面的叫做pre-cursor干扰。 DFE的第一个系数 h1 (此例中0.175)矫正第一个post-cursor,第二个系数 h2 (此例中0.075)矫正第二个post-cursor。 Various embodiments provide for correcting pre-cursor intersymbol interference (ISI) and post-cursor ISI in a data signal received over a channel. More particularly, some embodiments

Today while working with IDLE I encountered a very long response from claude-3.7-sonnet-thinking, agent mode. I thought the problem was in my PC, rebooted and after

文章浏览阅读6w次,点赞46次,收藏329次。本文深入探讨了高速信号传输中预加重和去加重技术的重要性。预加重通过在信号源头增强高频分量来补偿传输过程中的高频衰 SerDes channel equalization techniques are employed to overcome the intersymbol interference for serial interfaces for design compliance.

Recent enhancements to the upcoming IBIS standard now support backchannel training, enabling IBISAMI models to emulate this real-world SerDes behavior.

图19 DFE原理 DFE是通过检测前面波形状态来补偿后续波形,导致其不能对前面的波形进行补偿。 因此DFE能够消除Post-Cursor导 A programmable pre-cursor ISI equalizer combined with a 3-tap DFE is implemented to work at 10-Gb/s and compensate the channel loss of -20 dB. The results show it outperform a Abstract-This paper describes the design of pre-insertion resistor (PIR) for mitigation of ‘zero missing’ phenomenon (ZMP) observed in circuit breakers where the current does not cross

DS250DF230 has EQ bypass option on one of the CTLE stages, which allows it to be used in lower insertion loss cases than DS250DF210. DS250DF230 can output a recovered

This application note discusses key features of the redriver relevant to the PCIe negotiation and provides pre- and post- channel loss analysis to help fine-tune and facilitate redriver CTLE Astera Labs‘ Casey Morrison presented on simulating with retimers for PCIe 5.0 at DesignCon 2020. View the paper and slides.

- Drive Medical Deltarollator Triwalker

- Dubai Marina To Old Town Ferry

- Drohneneinsatz Netze Bw Testet Fireflies Für Vogelschutz

- Duck Commander To Sponsor Indepedence Bowl

- Droit De Regard En Replay – REPLAY EMISSIONS: toutes les vidéos à revoir

- Duales Studium Gls Germany Gmbh

- Dry Cleaning: New Long Leg Album Review

- Dubai Frame: Tickets, Timings _ Visit Dubai Frame: What You Need To Know

- Ducati.Diag Freeware – TPS reset or tune around it?

- Dublin Vs Mayo Tv And Live Stream Info For Saturday’S Game

- Drone Wallpapers – Drone wallpapers hd, desktop backgrounds, images and pictures

- Drk-Landesverband Sachsen-Anhalt E.V.

- Drop A Size In A Week! 7 Super Effective Exercises To Lose Fat