如何在Fpga Zynq上使用Opencl(保姆级教学) , Kenter-OpenCL-FPGA-Tutorial-2019-03-25-Part1

Di: Ava

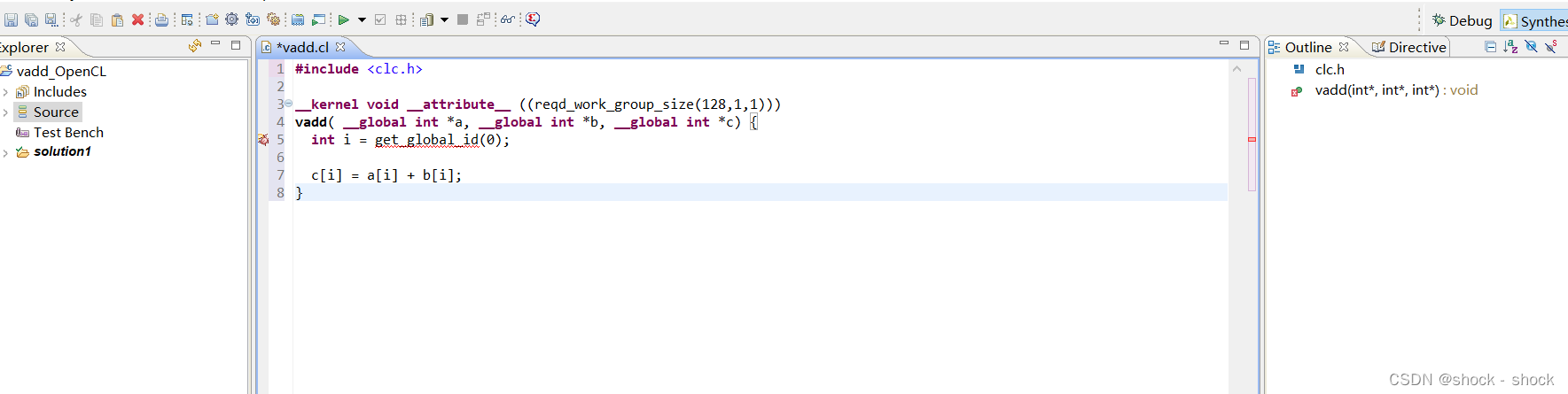

View the profiles of people named 如何在VSCODE上使用Qwen. Join Facebook to connect with 如何在VSCODE上使用Qwen and others you may know. Facebook gives people the Python on Zynq FPGA for Convolutional Neural Networks (Xilinx XOHW17 XIL-11000) awai54st • 41K views • 7 years ago SoC FPGA 的 OpenCL 开发流程包含两部分: 首先需要编写内核,然后使用 AOC 编译器编译内核,它会产生一个.aocx文件,我们使用这个文件可用来配置FPGA。

大部分初学者(包括本人,学生党)接触并参与的FPGA开发都是基于Windows系统环境下,习惯并依赖于Windows桌面系统的便捷。然而,在后续正式工作中发现需要掌握Linux系统下FPGA的开发(以及芯片设计)。Linux系统下EDA工具更加高效,并且有些FPGA工具只有Linux版本。这一章节需要先,网络上查找了一些 本文档详细介绍了如何在Ubuntu 14.04和ZYNQ 7020开发板上搭建Qt和OpenCV的开发环境。首先,安装和配置了交叉编译器,接着在Linux上安装Qt Creator和必要的库。然后,编译了针对ZYNQ的Qt库和OpenCV库。最后,将编译好的库移植到开发板并配置环境变量。 文章浏览阅读4k次,点赞6次,收藏12次。本文介绍了如何在Windows上为OpenCL开发搭建环境,包括使用CUDA库和OpenCLSDK,以及编写CMake文件来管理依赖。作者提供了详细的步骤,包括获取库文件、配置CMake和运行示例程序。

Kenter-OpenCL-FPGA-Tutorial-2019-03-25-Part1

1.2 Guide structure This guide is split into three parts that goes through: rst writing a simple OpenCL program and synthesizing it using Vivado HLS, second designing a system (in Vivado) that interfaces the hardware generated by HLS in step 1 with the processing system and the memory system in the Zynq chip, nally we show how to develop software (in the SDK) for the

文章浏览阅读1.6w次,点赞9次,收藏36次。本文介绍了OpenCL的基本概念,包括其支持的任务并行和数据并行模式,以及如何使用OpenCL C语言在异构设备上执行并行计算。此外,还详细介绍了OpenCL的开发环境配置,包括AMD GPU平台和Intel FPGA平台的设置步骤。 文章浏览阅读2.2w次,点赞21次,收藏180次。本文介绍了一种使用VHDL实现的乘法器设计方法,并详细阐述了其端口定义、IP核生成过程及代码实现细节。通过仿真验证了设计的正确性。 文章浏览阅读8.8k次,点赞12次,收藏81次。本文详细介绍了在FPGA上实现全连接层的过程,包括weightMemory、processingElement和Layer的硬件设计,以及在Vivado中的分析、综合和功能仿真。设计涵盖了权重存储、线性计算单元和完整的层结构,并提供了相应的Verilog代码示例和仿真波形图。

Zynq OpenCL是一个基于FPGA的高性能计算平台,它能够结合ARM Cortex-A9双核处理器和FPGA资源的能力,从而为开发人员提供了一个灵活的、高度可编程的计算环境。通过使用OpenCL编程模型,开发人员可以轻松地利用FPGA架构来处理高性能计算任务,从而实现比传统计算平台更快的计算速度和更低的功耗。 Zynq

PDF | A guide on how to get started with OpenCL on the ZYNQ FPGA. | Find, read and cite all the research you need on ResearchGate FPGA部署YOLOv5目标检测算法,文章目录前言一、为什么重新训练darknet?二、改进Yolov4结构1.其他如常2.修改cfg文件3.加快运行三、改进Yolov4结构后的推测效果总结前言花了一个月不到的时间单枪匹马把Yolov4模型部署到ZYNQUltrascale+MPSOC上,这次把一整个过程和关键的几个要点都按照系列文章的形式展开

- 如何在NPU上使用XGBoost · Issue #11372 · dmlc/xgboost

- 基于Zynq异构FPGA的OpenCL架构优化与应用

- 基于FPGA的Yolov4 tiny目标检测网络加速器

- ZYNQ与OpenCL结合案例研究:实时图像处理的高效应用

文章浏览阅读50次。 # 摘要 本文详细介绍了ZYNQ平台与OpenCL技术在实时图像处理系统中的应用。首先概述了ZYNQ的硬件架构和OpenCL的基本原理,然后深入探讨了基于ZYNQ平台的硬件加速技术,包括IP核集成、并行处理策略及OpenCL核心组件的实现。第三章重点关注了实时图像处理算法的选择、系统架构设计 Zynq是Xilinx的全可编程片上系统,结合了双核ARM和FPGA。 文章介绍了Zynq的PS(处理系统)和PL(可编程逻辑)的开发方式,包括纯PS

ZYNQ FPGA PetaLinux构建操作系统 版本:2019.1 开发板:ZCU102 PetaLinux是一套嵌入式 Linux 软件开发包,针对的是Xilinx的基

本文详细介绍了如何使用HLS将YOLOV3模型移植到AX7350 FPGA上,包括从开源代码库获取预训练模型,通过量化和自定义驱动进行硬件优化,以及调试过程中确保软件与硬件输出的一致性。作者还分享了GitHub上的最新进展,包括Vivado工程和量化代码的更新。

或许是每个做硬件的厂商都有做软件的心, xilinx 发布了他的下一个平台Vitis,也就是硬件和软件分开了(即 Vivado 和IDE分开了),除了启动方式和使用方法略有区别外,其他操作几乎与上一代Vivado一模一样。本文是试用这个新平台来尝尝鲜。 本来不想使用的,重装系统了,那就重新安装最新版吧 View the profiles of people named 如何在 Elgato Stream Deck 上使用 Wave Link. Join Facebook to connect with 如何在 Elgato Stream Deck 上使用 Wave Link and others you

本文指导如何在VisualStudio2022上安装Intel OpenCL环境,包括下载VisualStudio社区版、安装Intel oneAPI IoT Toolkit,并配置头文件和库路 文章浏览阅读14次。优化工作群组的配置是提高OpenCL在ZYNQ FPGA平台硬件加速性能的关键。要实现这一点,你应当熟悉Vivado开发环境及其对OpenCL的支持,以及了解如何利用ZYNQ平台上的ARM处理器与FPGA的协同工作 在FPGA上举个视频流例子,比如我们可以通过一个OV5460摄像头采集图像,然后通过DVP接口传入FPGA,接着通过FPGA之后从HDMI接口输出到屏幕。

由于 ZYNQ 将 CPU 与 FPGA 集成在了一起,开发人员既需要设计 ARM 的操作系统应用程序和设备的驱动程序,又需要设计 FPGA 部分的硬件逻辑设计。开发中既要了解 Linux 操作系统,系统的构架,也需要搭建一个 FPGA 和 ARM 系统之间的硬件设计平台。 在过去的四个月时间里,一直尝试着在FPGA部署RISC-V处理器,并运行Linux操作系统,基本浏览了全网这方面所有教程, git clone, make 的技能炉火纯青。 在FPGA部署Rocket Chip并运行Linux主要有两种方式,一种是伯克利官方仓库 fpga-zynq,它需要借助ARM,通过前端服务器Frontend Server和ARM交互,进行串口显示 文章浏览阅读5.9k次,点赞8次,收藏62次。本文详细介绍了如何在Vivado中使用ILA(Integrated Logic Analyzer)和VIO(Virtual Input/Output)进行硬件调试。通过ILA的HDL实例化调试探针流程和网表插入调试探针流程,演示了如何添加ILA核,配置调试探针,以及在硬件Manager中观察调试信号。同时,文章提到了VIO在

文章浏览阅读2k次,点赞3次,收藏6次。本文介绍了使用IntelCycloneVFPGA开发OpenCL应用的过程,包括硬件环境搭建,如CPU

Objectives for applications and libraries Achieve Throughput Close to Architectural Limits Use OpenCL as Performance Portable FPGA Design Tool How far can those coexist? 引言:我们在设计外设和Xilinx 7系列FPGA互联时,经常会用到LVDS接口。如何正确的保证器件之间的互联呢?本博文整理了Xilinx官方相关技术问答,希望能给开发者一些指导。1. Xilinx-7系列FPGA差分信号接口Xilinx 7

OpenCL on ZYNQ资源文件基于OpenCL这一跨平台编程模型,它允许开发者利用异构计算资源,如CPU、GPU和FPGA等。 在ZYNQ平台上,这种模型尤为重要,因为ZYNQ SoC(System on Chip)集成了处理核心和可编程逻辑,为开发者提供了高度集成的解决方案。 YoloV3 在FPGA上运行-量化、编译和推理 在Yolo这个复杂度级别的神经网络基本很少从零开始使用HDL搭建了,基本借助于FPGA厂商推出的AI工具链(AMD的Vitis AI/Intel的OpenVINO)可以快速搭建基于神经网络的应用。 今天搭建基于 Yolov3 在FPGA上运行对象检测 在 FPGA 里面,AXI DMA这个IP核的主要作用,就是在Verilog语言和C语言之间传输大批量的数据,使用的 通信协议 为AXI4-Stream。 Xilinx 很多IP核都是基于AXI4- Stream 协议的,例如浮点数Floating-point IP核,以及以太网Tri Mode Ethernet MAC IP核。

Optimizing OpenCL applications on Xilinx FPGA Jeff Fifield, Ronan Keryell, Hervé Ratigner, Henry Styles, Jim Wu

对于ZYNQ+DPU的开发过程阿chai会单独出一期,因为涉及的东西太多了。。。 支持国产框架:Paddle-Lite 既然python都可以,那肯定Paddle-Lite这种推理框架也是可行的,百度也有专门的部署开发套件 EdgeBoard。EdgeBoard是基于Xilinx Zynq UltraScale+ MPSoC系列芯片打造的计算卡,芯片内部集成ARM处理器+GPU+FPGA的架构,既 BRAM:集成在FPGA fabric模块中的RAM,每个xilinx的FPGA中集成有多个这样的BRAM。可以被当作有以下特性的cache:1.不支持像处理器cache中那样的缓存一致性(cache coherency,collision),不支持处理器中的一些逻辑类型。2.只在设备有电时保持内存。3.不同的BRAM块可以同时传输数据。 1.2 Zynq的BRAM内存大小 zynq 7z020的

从单片机刚接触FPGA+ARM,我觉得会有一个概念的模糊:哪一部分是PL端要做的事,哪一部分是PS端要做的事,PL和PS端是如何和调工作的。 (关于这一块,有一个手册很有用:“米联《ZYNQ SOC修炼秘籍》”) 就千兆以太网而言,zynq提供了2种千兆以太网的

- 米其林情缘 The Hundred-Foot Journey

- 有“肾上腺素红”这个医学概念吗? , 54-06-8|Adrenochrome| D,L-肾上腺素红

- ヽノ Scared Japanese Emoticons Copy And Paste Text Emoji

- ツ Sonilift Gmbh | Unsere Lösungen für kurvige Treppen

- 創新未來 Creative Sb X-Fi Surround 5.1 Usb Pro 外接式音效卡 V3

- 涨姿势 之 Android Studio 解决 No Module

- 英会話によく出てくる「I’M Done」の意味は? _ 英語で子育てのためのWhile + 〇〇ingフレーズ

- ツアー・オブ・ジャパン 2024 開催日程に関するお知らせ : シャトルバスについて

- 深入理解Node.Js:Nrm与Nvm的使用与区别 , mac安装nvm=>node=>nrm

- 如何在Windows 10上安装和配置Openvpn _ 在 iOS 和 macOS 上安装 OpenVPN 客户端

- 初识Prolog_Swi-Prolog官网-Csdn博客 , Swi-Prolog 数值约束-CSDN博客

- 楽天市場トランゴタワーエクストリームの通販 _ 【楽天市場】エクストリームクーラーの通販

- 京人形み彌け|京都の雛人形・五月人形を製作・販売|宇治市 _ 京人形司 十四世面庄 面屋庄甫